## ACS APPLIED MATERIALS & INTERFACES

# Ordered Silicon Microwire Arrays Grown from Substrates Patterned Using Imprint Lithography and Electrodeposition

Heather A. Audesirk,<sup>†</sup> Emily L. Warren,<sup>†,‡</sup> Jessie Ku,<sup>§</sup> and Nathan S. Lewis\*

Beckman Institute and Kavli Nanoscience Institute, 210 Noyes Laboratory, 127-72, Division of Chemistry and Chemical Engineering, California Institute of Technology, Pasadena, California 91125, United States

**Supporting Information**

**ABSTRACT:** Silicon microwires grown by the vapor—liquid—solid process have attracted a great deal of interest as potential light absorbers for solar energy conversion. However, the research-scale techniques that have been demonstrated to produce ordered arrays of micro and nanowires may not be optimal for use as high-throughput processes needed for large-scale manufacturing. Herein we demonstrate the use of microimprint lithography to fabricate patterned templates for the confinement of an electrodeposited Cu catalyst for the vapor—liquid—solid (VLS) growth of Si microwires. A reusable polydimethylsiloxane stamp was used to pattern holes in silica sol—gels on silicon substrates, and the Cu catalyst was electrodeposited into the holes. Ordered arrays of crystalline p-type Si microwires were grown across the sol—gel-patterned substrates with materials quality and performance comparable to microwires fabricated with high-purity metal catalysts and cleanroom processing.

KEYWORDS: imprint lithography, electrodeposition, VLS, silicon microwire, photoelectrochemistry

**S** ilicon microwire (Si MW) and nanowire arrays have a wide range of potential applications for solar energy conversion<sup>1,2</sup> and as components for the next generation of microelectronic and optoelectronic devices.<sup>3</sup> Although the growth and material quality of these arrays has been wellcharacterized in recent years, few reports have discussed how this technology can be scaled up for large-area manufacturing.<sup>4</sup> The vapor-liquid-solid (VLS) method used to produce Si MW arrays is a robust and scalable approach to the growth of crystalline materials from gaseous precursors.<sup>5</sup> Specifically, the ability to directly produce high-quality, single-crystalline semiconducting material from a low-cost precursor at atmospheric pressure, without the need for further purification or wafering, makes SiCl<sub>4</sub> VLS growth an interesting approach for the production of Si for energy-conversion applications.<sup>6-8</sup>

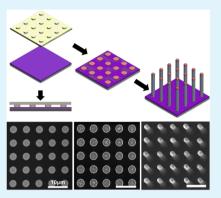

The Si(111) substrate used to produce single-crystal epitaxial growth in the VLS process can be reused if the wires are peeled off in a flexible polymer film and a catalyst metal is subsequently electrodeposited into the remaining oxide pattern.<sup>9,10</sup> However, in all prior reports, the formation of the patterned template relies on high-temperature and high-vacuum processes. For example, oxide-coated (111)-oriented Si growth wafers have been photolithographically patterned to introduce a confining layer that prevents the catalyst droplets from aggregating during VLS growth, and controls the spacing and diameter of the resulting Si microwires (Figure 1).<sup>11</sup> The VLS catalyst material (usually Cu, 99.999%) was then deposited across the entire wafer via thermal evaporation under high vacuum, and the excess metal removed by lift-off in acetone.<sup>11,12</sup> The demonstration that scalable and low-cost patterning and catalyst-deposition techniques can be used to

Figure 1. Fabrication process for the growth of Si MW arrays using traditional photolithography and metal catalyst deposition by evaporation. A thermal oxide is (A) grown on a Si wafer (B), coated with photoresist, and (C) patterned using photolithography. (D) A conformal layer of Cu is evaporated over the sample, and then (E) lifted off to leave a patterned substrate for VLS growth. (F) Wires are then grown from SiCl<sub>4</sub> using the VLS process.

produce controlled microstructures is an important step in the development of scalable Si MW and nanowire technologies. Herein, we report the VLS growth of uniform, positioncontrolled Si microwires from electrodeposited Cu catalysts on substrates patterned using imprint lithography. Furthermore, we show using photoelectrochemistry that Si MW arrays grown by this method have material quality similar to arrays grown on

Received:October 17, 2014Accepted:January 6, 2015Published:January 6, 2015

ACS Publications © 2015 American Chemical Society

#### **ACS Applied Materials & Interfaces**

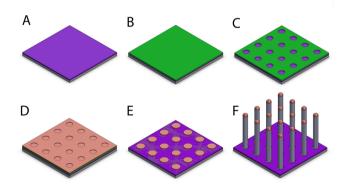

substrates prepared with photolithography and high-vacuum metal evaporation. In the present work, we use microimprint lithography, along with subsequent electrodeposition of the metal catalyst, as the process steps used to form a patterned template for VLS-catalyzed Si microwire growth on Si substrates (Figure 2).

Figure 2. Fabrication process for the growth of Si MW arrays using microimprint lithography and electrodeposition of the metal catalyst. (A) Sol–gel layer is spun onto a Si wafer at a thickness corresponding to that of the imprint stamp, and (B) the stamp is pressed into the sol–gel. (C) Stamp is removed, leaving a pattern of holes in the sol–gel, into which (D) Cu is electrodeposited. (E) Wires are then grown from SiCl<sub>4</sub> using the VLS process.

Soft lithography has been used to pattern features less than 100 nm in size, and provides a scalable alternative to traditional photolithography.<sup>13–15</sup> In our work, microimprint lithography of a silica sol-gel was used to create the patterned confining layer on the VLS growth templates. To create the stamp used in the microimprint process, a master was fabricated by photolithographically patterning a thermal SiO<sub>2</sub> layer on a Si wafer. The thickness of the oxide layer was chosen to be the same as the desired thickness of the sol-gel confining layer  $(\sim 150 \text{ nm})$ , with the pattern specifically consisting of a squarepacked array of 3  $\mu$ m diameter holes spaced 7  $\mu$ m from center to center  $(3 \times 7 \ \mu m^2 \text{ pitch})$ . The stamp master was then used to produce a bilayer polydimethylsiloxane (PDMS) stamp that combined a rigid stamping interface with a flexible substrate that allowed for conformal patterning. Each silicon master can be used to produce a large number of flexible PDMS stamps, and each PDMS stamp can be used many times to pattern solgel-coated wafers. The rigid stamping PDMS (hereafter referred to as x-PDMS) allowed the stamp to reproduce, with high fidelity, features on the scale of tens of nanometers, whereas the malleable stamp body provided the flexibility necessary to make conformal contact with the substrate.<sup>16</sup>

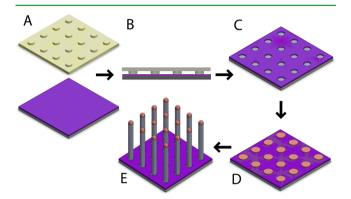

Before patterning, each Si(111) VLS growth wafer was etched in buffered hydrofluoric acid (BHF), to remove any native oxide. A uniform ~150 nm thick layer of sol–gel was then produced by spin-coating a silica sol–gel onto the wafer. While the sol–gel was still wet, the bilayer PDMS stamp was carefully applied by hand to cover the entire wafer (Figure 2B). Substrate conformal imprint lithography (SCIL), in which the stamp is attached by a vacuum to a plate that contains a series of grooves that pressurize sequentially to ensure conformal contact between stamp and wafer, and thereby eliminate the defects and air bubbles that are introduced when stamping by hand, could also be used.<sup>17,18</sup> The sol–gel material was allowed to cross-link at room temperature for ~1 h, and the stamp was carefully removed, resulting in a patterned sol-gel layer. Figure 3 depicts atomic-force microscopy (AFM), scanning-electron

**Figure 3.** Patterned silica sol-gel on a Si wafer (square packed  $3 \times 7$   $\mu$ m array of holes): (a) AFM image, (b) SEM micrograph, (c) height measurements from a profilometry line scan.

microscopy (SEM), and contact profilometry images of the templated growth wafers produced by the microimprint lithography process. Using this technique, wafers up to 4" in diameter could be patterned by hand. Because of the flexible nature of the stamp, when macroscopic defects such as air bubbles or dust particles were present, the pattern quality was only affected locally (over a range of  $\mu$ m to mm from the defect), so the stamp was replicated in the sol–gel over >90% of the substrate even when the substrates were not patterned in a cleanroom.

During the VLS growth process, the patterned substrate is exposed to 1000 °C and to flowing  $H_2(g)$  and SiCl<sub>4</sub>(g). These conditions create HCl(g) as a byproduct, and therefore require a robust patterned confining layer. To determine whether the sol-gel would retain its pattern fidelity during the wire-growth process, pieces of a patterned Si wafer were annealed under  $N_2(g)$  for 20 min at temperatures between 100 and 1000 °C. Profilometry of the annealed samples showed a slight densification of the sol-gel, but indicated the general retention of the stamped pattern. A substrate chip with a patterned solgel (but without the VLS growth catalyst) was also placed into the chemical-vapor deposition (CVD) reactor and sent through the growth process with all variables intact, except for the absence of  $SiCl_4(g)$  and  $BCl_3(g)$  during the "growth" phase of the process. Despite the gas flows and high temperatures, a slight compaction (<10%) of the sol-gel was observed but the pattern fidelity remained high, confirming that the sol-gel could be used to replace the confining thermally grown SiO<sub>2</sub> layer that has been previously used to produce Si microwire arrays.11

The VLS growth process also requires use of a metal catalyst, typically either Cu, Ni, or Au. The purity of the metal used as the VLS catalyst affects the device performance of the resulting Si MW arrays.<sup>19,20</sup> Cu impurities are less detrimental than Au impurities to the performance of both planar and microwire Si solar cells, motivating the investigation of electrodeposited Cu

### **ACS Applied Materials & Interfaces**

as an alternative VLS catalyst.<sup>21,22</sup> We therefore focused our effort on enabling the use of Cu for the growth of VLS-catalyzed Si MW arrays.

To achieve conformal electrodeposition of Cu and thus highquality VLS Si MW growth, the sol-gel was first densified by baking the substrate on a hot plate at 150 °C for 20 min, and then the residual sol-gel and native oxide were removed from the patterned holes by dipping the substrate in dilute HF (aq, 1% by volume). Although the sol-gel slowly etches in HF(aq), careful control over the duration of this etch allowed for exposure of the conductive Si substrate at the bottom of the holes while not impacting the quality of the SiO<sub>2</sub> confining layer elsewhere.

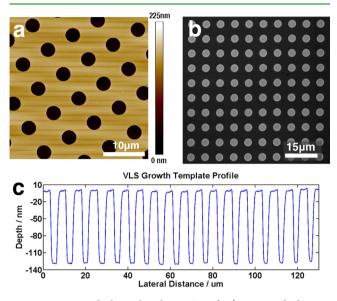

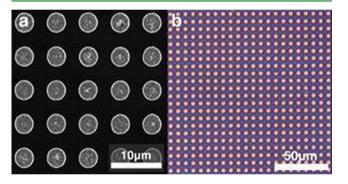

Immediately after etching, the patterned wafer was placed into a pressed electrodeposition cell that had been filled with a commercially available copper electrodeposition solution (see Figure S1 in the Supporting Information). A high-purity Cu (99.9999%) rod served as the counter electrode. Cu was then deposited potentiostatically at -1.05 V vs Ag/AgCl until the desired charge density had been passed. Optical microscopy and SEM images indicated that the Cu deposited selectively in the holes in the patterned overlayer, with excellent fidelity across large (>3 cm<sup>2</sup>) areas (Figure 4).

**Figure 4.** (a) SEM and (b) optical images of electrodeposited copper in patterned sol–gel. Diameter =  $3.5 \ \mu m$ , pitch =  $7 \ \mu m$ .

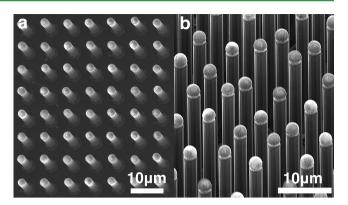

Samples were then placed into the CVD reactor, to grow ptype Si MW arrays. Wire growth was performed at 1000 °C in  $H_2(g)$ , using SiCl<sub>4</sub>(g) as the Si precursor and BCl<sub>3</sub>(g) as the ptype dopant source. The passage of ~0.2 C cm<sup>-2</sup> of charge density during Cu electrodeposition resulted in wires that were 2  $\mu$ m in diameter. The diameter of the wires depended on the diameter of the hemispherical catalyst eutectic droplet formed during growth, hence the wire diameter was different than that of the catalyst island.<sup>12</sup> The dopant density of the wires was ~6  $\times$  10<sup>17</sup> cm<sup>-3</sup>, as measured using a 4-point probe technique.<sup>23</sup> The wires grown from the electrodeposited catalyst exhibited uniformity across the growth substrate comparable to substrates patterned with photolithography (Figure 5). The amount of electrodeposited copper determined the diameter of the resulting Si MWs, hence given the flexibility afforded by electrodeposition, large amounts of material could be quickly and easily deposited to thereby permit the controlled growth of Si MWs of various diameters (see the Supporting Information).

To evaluate the electrical performance of the microwire arrays, the wires were cleaned using an RCA2 etch to remove the Cu growth catalyst and other impurities, and the substratesupported wire arrays were then processed and made into electrodes. Additional processing was required for evaluation of

Figure 5. SEM micrographs of Si MW arrays grown from electrodeposited Cu and silica sol-gel patterned substrates. (a) Top down view of as-grown wires (before catalyst removal), (b) 45° tilt view of as-grown Si MW array.

the performance of MWs on the Si substrate, because the degenerately doped growth wafer and the microwire bases can provide pathways for shunting during electrochemical testing of the performance of the Si MW arrays. To protect these interfaces from the electrolyte, an oxide boot was formed on the microwires (see Figure S2 in the Supporting Information), by growth of a  $\sim$  150 nm thick thermal oxide over the entire surface of the sample at 1000  $\,^{\circ}\mathrm{C}$  for 2 h.  $^{24}$  The oxide was selectively protected at the wire bases and growth substrate, and was etched off everywhere else. This oxidation process is also thought to act as a getter for metallic impurities incorporated at the surface of the wires as a result of the metal-catalyzed growth process, and etching of this oxide layer is equivalent to removing the outer 50-100 nm of the metal-rich Si surface layer and results in improved photoelectrochemical performance of the wire arrays.

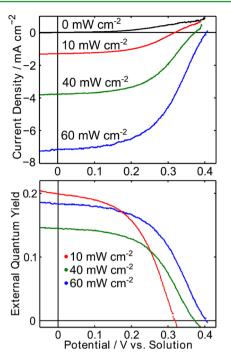

The resulting Si MW arrays were then made into electrodes, and tested for their photoelectrochemical performance in contact with a 50 mM solution of the one-electron, reversible, methyl viologen  $(MV^{2+/+})$  redox couple.<sup>25,26</sup> The  $MV^{2+/+}$  redox couple makes a conformal, high barrier-height contact to p-type Si, and has been used to study the performance of similar p-Si MW arrays (see the Supporting Information for experimental details and controls).<sup>1,24</sup> At normal incidence under 60 mW cm<sup>-2</sup> of 808 nm illumination (which produces a similar photon flux above the Si band gap as that obtained from broadband, 100 mW cm $^{-2}$ , AM 1.5G solar illumination), the champion Si MW electrode grown from microimprint/electrodeposition exhibited an open-circuit voltage ( $V_{\rm oc}$ ) = 400 ± 7 mV, a shortcircuit current density  $(J_{sc}) = 6.8 \pm 0.5$  mA cm<sup>-2</sup>, an external quantum yield at short circuit ( $\Phi_{\rm ext,sc}$ ) = 0.17 ± 0.02, a fill factor (ff) = 0.52  $\pm$  0.03 and an energy-conversion efficiency ( $\eta_{808}$ ) =  $2.4 \pm 0.2\%$  (Figure 6). Averaging across six devices, the figures of merit for the Si microwire arrays under investigation were  $V_{\rm oc} = 380 \pm 10 \text{ mV}, J_{\rm sc} = 7 \pm 2 \text{ mA cm}^{-2}, \Phi_{\rm ext,sc} = 0.17 \pm 0.05,$ ff = 0.5  $\pm$  0.1, and  $\eta_{808}$  = 2.1  $\pm$  0.3%. These figures of merit are comparable to those of Si microwires grown from photolithographically patterned oxide templates and thermally evaporated high-purity Cu, with the largest difference arising from the open-circuit voltage, which was only ~30 mV smaller than that observed for wires grown with 6N Cu.<sup>1</sup> This trend contrasts with that observed for Au-catalyzed Si MW arrays, in which a slight decrease in the purity of the Au used (5N vs 6N) led to a significant reduction in the photoelectrochemical energyconversion efficiency of the resulting Si MW arrays.<sup>20</sup>

Figure 6. (Top) J-E data and (bottom) external quantum yield for Si MW array electrodes tested in 50 mM  $MV^{2+/+}$  electrolyte under 808 nm illumination.

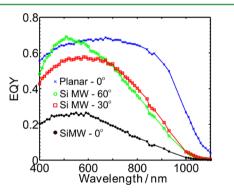

The external quantum efficiency of the electrode for wavelengths from 400 to 1100 nm was measured as a function of the angle of incidence of light relative to the surface of the Si substrate. As shown in Figure 7, measurements were obtained

Figure 7. Spectral response of p-Si MW array and planar p-Si electrodes measured in methyl viologen electrolyte. Data were obtained under potentiostatic conditions at the light-limited photocurrent (-0.5 V vs SCE).

at 0 (approximately normal to the array), 30, and 60°, respectively. The spectral response of the wire arrays that were grown from the templating method described herein was nearly identical to that of wire arrays grown from 6N Cu with the pattern introduced into a thermal SiO<sub>2</sub> overlayer using photolithography.<sup>27</sup>

In summary, a scalable, low-cost, and low-energy fabrication technique for the growth of vertically oriented silicon microwire arrays has been demonstrated, resulting in the production of Si microwire arrays with essentially equivalent electrical performance to wire arrays produced using traditional high-energy, higher-cost fabrication methods. Patterning of the growth substrate was accomplished via microimprint lithography using a silica sol-gel, and catalyst deposition was achieved by potentiostatic electrodeposition from commercially available Cu electrodeposition solutions. This fabrication method is both scalable and robust, allowing for the creation of Si microwire arrays of varying pitch and wire diameter, which can potentially lead to the fabrication of more efficient photocathodes for the hydrogen-evolution reaction (HER) and/or form the basis for new sensors and battery electrodes made from Si microwire and nanowire arrays.

## ASSOCIATED CONTENT

#### Supporting Information

Detailed experimental methods including the fabrication of the microimprint stamps, the electrodeposition of Cu, and the processing of the wire arrays are provided. This material is available free of charge via the Internet at http://pubs.acs.org.

## AUTHOR INFORMATION

## Corresponding Author

\*E-mail: nslewis@caltech.edu. Tel: +1 626 395 6335.

## **Present Addresses**

<sup>‡</sup>E.L.W. is currently at the National Renewable Energy Laboratory, 15013 Denver West Parkway, Golden, CO 80401 <sup>§</sup>J.K. is currently at Department of Materials Science and Engineering, Northwestern University, 2220 Campus Drive, Evanston, IL 60208, USA

#### **Author Contributions**

<sup>†</sup>These authors contributed equally.

The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work was supported by the National Science Foundation (Grant NSF-1214152), BP, the Gordon and Betty Moore Foundation, and DARPA. H.A.A. also acknowledges partial support from Dow Chemical. This work was partially performed at the Kavli Nanoscience Institute at the California Institute of Technology.

### ABBREVIATIONS

- VLS, vapor-liquid-solid

- Si MW, silicon microwires

- PDMS, polydimethylsiloxane

- BHF, buffered hydrofluoric acid AFM, atomic-force microscopy

- AFM, atomic-force microscopy

- SCIL, substrate conformal imprint lithography

- SEM, scanning-electron microscopy

- CVD, chemical-vapor deposition

## REFERENCES

(1) Boettcher, S. W.; Spurgeon, J. M.; Putnam, M. C.; Warren, E. L.; Turner-Evans, D. B.; Kelzenberg, M. D.; Maiolo, J. R.; Atwater, H. A.; Lewis, N. S. Energy-Conversion Properties of Vapor-Liquid-Solid-Grown Silicon Wire-Array Photocathodes. *Science* **2010**, 327, 185– 187.

(2) Putnam, M. C.; Boettcher, S. W.; Kelzenberg, M. D.; Turner-Evans, D. B.; Spurgeon, J. M.; Warren, E. L.; Briggs, R. M.; Lewis, N. S.; Atwater, H. A. Si Microwire-Array Solar Cells. *Energy Environ. Soc.* **2010**, *3*, 1037–1041.

#### **ACS Applied Materials & Interfaces**

(3) Yan, R.; Gargas, D.; Yang, P. Nanowire Photonics. *Nat. Photon* **2009**, *3*, 569–576.

(4) Heurlin, M.; Magnusson, M. H.; Lindgren, D.; Ek, M.; Wallenberg, L. R.; Deppert, K.; Samuelson, L. Continuous Gas-Phase Synthesis of Nanowires with Tunable Properties. *Nature* **2012**, 492, 90–94.

(5) Wagner, R. S.; Ellis, W. C. Vapor-Liquid-Solid Mechanism of Single Crystal Growth. *Appl. Phys. Lett.* **1964**, *4*, 89–90.

(6) Kendrick, C. E.; Redwing, J. M. The Effect of Pattern Density and Wire Diameter on the Growth Rate of Micron Diameter Silicon Wires. *J. Cryst. Growth* **2011**, 337, 1–6.

(7) Kim, D. R.; Lee, C. H.; Rao, P. M.; Cho, I. S.; Zheng, X. L. Hybrid Si Microwire and Planar Solar Cells: Passivation and Characterization. *Nano Lett.* **2011**, *11*, 2704–2708.

(8) Tian, B. Z.; Zheng, X. L.; Kempa, T. J.; Fang, Y.; Yu, N. F.; Yu, G. H.; Huang, J. L.; Lieber, C. M. Coaxial Silicon Nanowires as Solar Cells and Nanoelectronic Power Sources. *Nature* **2007**, *449*, 885–U8.

(9) Plass, K. E.; Filler, M. A.; Spurgeon, J. M.; Kayes, B. M.; Maldonado, S.; Brunschwig, B. S.; Atwater, H. A.; Lewis, N. S. Flexible Polymer-Embedded Si Wire Arrays. *Adv. Mater.* **2009**, *21*, 325–328.

(10) Spurgeon, J. M.; Plass, K. E.; Kayes, B. M.; Brunschwig, B. S.; Atwater, H. A.; Lewis, N. S. Repeated Epitaxial Growth and Transfer of Arrays of Patterned, Vertically Aligned, Crystalline Si Wires from a Single Si(111) Substrate. *Appl. Phys. Lett.* **2008**, *93*, 032112.

(11) Kayes, B. M.; Filler, M. A.; Putnam, M. C.; Kelzenberg, M. D.; Lewis, N. S.; Atwater, H. A. Growth of Vertically Aligned Si Wire Arrays over Large Areas (> 1 cm<sup>2</sup>) with Au and Cu Catalysts. *Appl. Phys. Lett.* **2007**, *91*, 103110.

(12) Warren, E. L. Silicon Microwire Arrays for Photoelectrochemical and Photovoltaic Applications; California Institute of Technology: Pasadena, CA, 2013.

(13) Xia, Y. N.; Whitesides, G. M. Soft Lithography. Angew. Chem., Int. Ed. 1998, 37, 551-575.

(14) Guo, L. J. Nanoimprint Lithography: Methods and Material Requirements. *Adv. Mater.* 2007, *19*, 495-513.

(15) Campbell, C. J.; Smoukov, S. K.; Bishop, K. J. M.; Baker, E.; Grzybowski, B. A. Direct Printing of 3D and Curvilinear Micrometer-Sized Architectures into Solid Substrates with Sub-Micrometer Resolution. *Adv. Mater.* **2006**, *18*, 2004–2008.

(16) Odom, T. W.; Love, J. C.; Wolfe, D. B.; Paul, K. E.; Whitesides, G. M. Improved Pattern Transfer in Soft Lithography Using Composite Stamps. *Langmuir* **2002**, *18*, 5314–5320.

(17) Ferry, V. E.; Verschuuren, M. A.; van Lare, M. C.; Schropp, R. E. I.; Atwater, H. A.; Polman, A. Optimized Spatial Correlations for Broadband Light Trapping Nanopatterns in High Efficiency Ultrathin Film a-Si:H Solar Cells. *Nano Lett.* **2011**, *11*, 4239–4245.

(18) Ferry, V. E.; Verschuuren, M. A.; Li, H.; Schropp, R. E. I.; Atwater, H. A.; Polman, A. Improved Red-Response in Thin Film a-Si:H Solar Cells with Soft-Imprinted Plasmonic Back Reflectors. *Appl. Phys. Lett.* **2009**, *95*, 183503.

(19) Maiolo, J. R.; Kayes, B. M.; Filler, M. A.; Putnam, M. C.; Kelzenberg, M. D.; Atwater, H. A.; Lewis, N. S. High Aspect Ratio Silicon Wire Array Photoelectrochemical Cells. *J. Am. Chem. Soc.* **200**7, 129, 12346–12347.

(20) Santori, E. A.; Maiolo, J. R.; Bierman, M. J.; Strandwitz, N. C.; Kelzenberg, M. D.; Brunschwig, B. S.; Atwater, H. A.; Lewis, N. S. Photoanodic Behavior of Vapor-Liquid-Solid-Grown, Lightly Doped, Crystalline Si Microwire Arrays. *Energy Environ. Soc.* **2012**, *5*, 6867– 6871.

(21) Istratov, A. A.; Weber, E. R. Physics of Copper in Silicon. J. Electrochem. Soc. 2002, 149, G21-G30.

(22) Istratov, A. A.; Buonassisi, T.; McDonald, R. J.; Smith, A. R.; Schindler, R.; Rand, J. A.; Kalejs, J. P.; Weber, E. R. Metal Content of Multicrystalline Silicon for Solar Cells and its Impact on Minority Carrier Diffusion Length. *J. Appl. Phys.* **2003**, *94*, 6552–6559.

(23) Kelzenberg, M. D.; Turner-Evans, D. B.; Kayes, B. M.; Filler, M. A.; Putnam, M. C.; Lewis, N. S.; Atwater, H. A. Photovoltaic Measurements in Single-Nanowire Silicon Solar Cells. *Nano Lett.* **2008**, *8*, 710–714.

(24) Warren, E. L.; Boettcher, S. W.; Walter, M. G.; Atwater, H. A.; Lewis, N. S. pH-Independent, 520 mV Open-Circuit Voltages of Si/ Methyl Viologen(2+/+) Contacts Through Use of Radial n(+)p-Si Junction Microwire Array Photoelectrodes. J. Phys. Chem. C 2011, 115, 594–598.

(25) Lewis, N. S. A Quantitative Investigation of the Open-Circuit Photovoltage at the Semiconductor/Liquid Interface. *J. Electrochem. Soc.* **1984**, *131*, 2496–2503.

(26) Bird, C. L.; Kuhn, A. T. Electrochemistry of the Viologens. Chem. Soc. Rev. 1981, 10, 49-82.

(27) Boettcher, S. W.; Warren, E. L.; Putnam, M. C.; Santori, E. A.; Turner-Evans, D.; Kelzenberg, M. D.; Walter, M. G.; McKone, J. R.; Brunschwig, B. S.; Atwater, H. A.; Lewis, N. S. Photoelectrochemical Hydrogen Evolution Using Si Microwire Arrays. *J. Am. Chem. Soc.* **2011**, *133*, 1216–1219.